CMOS電路的最末級,通常是用顯現(xiàn)器顯現(xiàn),或者介入繼電器控制大電流,或者向遠處傳送信號等,很少沒有不借助晶體管的。

但是,在與這個晶體管接口時的困難不測地多。例如,由于與晶體管的基極連接的電阻過于小,從CMOS引出過大電流;或者電阻過大,使晶體管無法驅(qū)動。

下面對各種場所與晶體管的接口作以說明。

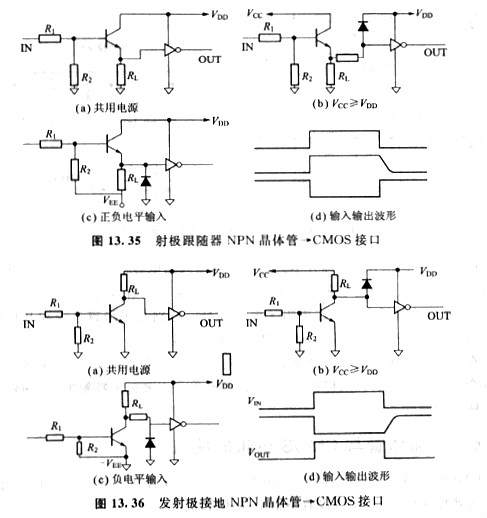

(1)發(fā)射極接地NPN晶體管→CMOS:圖l3.35(a)一(c)示出同~電源下,Vcc>VDD,Vcc

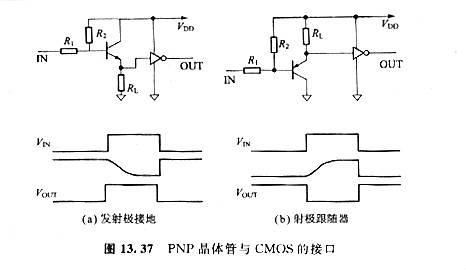

(2)射極跟隨器NPN晶體管→CMOS:與(1)的情況相反,在“L”電平常容易混入噪聲,存在從“L”向“H”時容易產(chǎn)生延遲的缺陷。圖13.36(a)一(c)示出接口例。

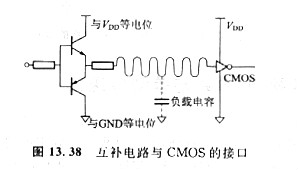

(3)發(fā)射極接地PNP晶體管→CMOS:如圖13. 37(a)所示,在降落時有延遲,在“L”電平要留意噪聲。

(4)射極跟隨器PNP晶體管→CMOS:其例子示于圖13. 37(b)。與(3)的情況相反,上升時產(chǎn)生延遲,“H”電平抗噪聲才干弱。

(5)互補電路→CMOS:在(1)~(4)的電路中,當(dāng)晶體管個CMOS的布線變長時,在“H”或者“L”電平,噪聲容易混入,由于布線電容而增大延遲時間。由于這些缺陷,所以對布線的長度有限制。這種情況下,運用圖13.38所示的互補電路使阻抗降落,關(guān)于改善噪聲和延遲時間有效果。

(6) CMOS→NPN晶體管:CM0S的輸出端由于負載過重而招致電流缺乏,或者耐壓缺乏的場所,需求這種接口。

由于經(jīng)過CMOS的p溝FET流出的電流(IOH)變成晶體管的基極電流,所以能夠驅(qū)動它的hfe的電流。進而在驅(qū)動大負載的場所,運用達林頓晶體管。

圖13. 39示出NPN晶體管驅(qū)動電路的例子。

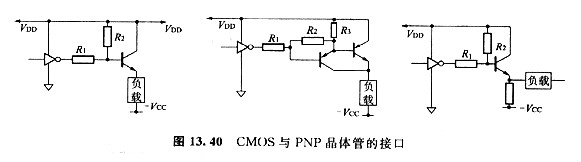

(7) CMOS→PNP晶體管:圖13. 40示出電路例。

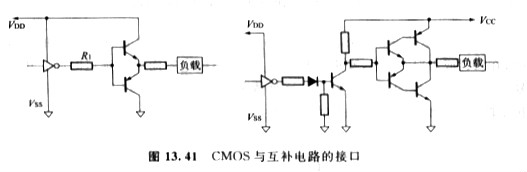

(8) CMOS→互補電路:將CMOS電路的信號向遠方傳送的場所,如前所述,為了抗噪聲、防止布線電容惹起的延遲,應(yīng)該采用互補電路。其接口例子示于圖13. 41。

烜芯微專業(yè)制造二極管,三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹