mos管

mos管與門電路圖,mos管是金屬(metal)、氧化物(oxide)、半導(dǎo)體(semiconductor)場效應(yīng)晶體管,或者稱是金屬—絕緣體(insulator)、半導(dǎo)體。MOS管的source和drain是可以對調(diào)的,他們都是在P型backgate中形成的N型區(qū)。在多數(shù)情況下,這個兩個區(qū)是一樣的,即使兩端對調(diào)也不會影響器件的性能。這樣的器件被認(rèn)為是對稱的。

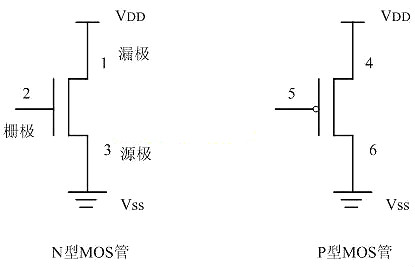

MOS管又分為兩種類型:N型和P型。如下圖所示:

以N型管為例,2端為控制端,稱為“柵極”;3端通常接地,稱為“源極”;源極電壓記作Vss,1端接正電壓,稱為“漏極”,漏極電壓記作VDD。要使1端與3端導(dǎo)通,柵極2上要加高電平。

對P型管,柵極、源極、漏極分別為5端、4端、6端。要使4端與6端導(dǎo)通,柵極5要加低電平。

在CMOS工藝制成的邏輯器件或單片機(jī)中,N型管與P型管往往是成對出現(xiàn)的。同時出現(xiàn)的這兩個CMOS管,任何時候,只要一只導(dǎo)通,另一只則不導(dǎo)通(即“截止”或“關(guān)斷”),所以稱為“互補(bǔ)型CMOS管”。

mos管與門電路圖及工作原理詳解

mos管與門電路圖-與門概述

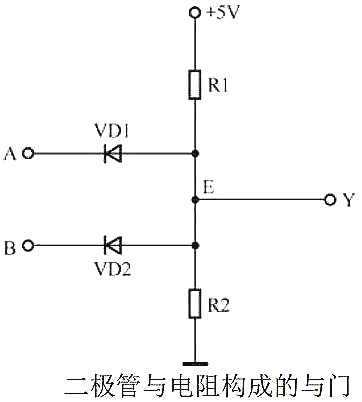

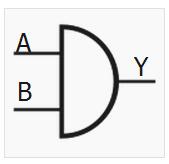

與門,又稱“與電路”、邏輯“積”、邏輯“與”電路。是執(zhí)行“與”運(yùn)算的基本邏輯門電路。有多個輸入端,一個輸出端。當(dāng)所有的輸入同時為高電平(邏輯1)時,輸出才為高電平,否則輸出為低電平(邏輯0)。

mos管與門電路圖-與門邏輯符號

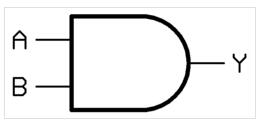

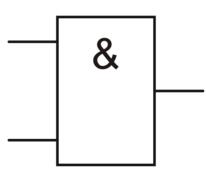

與門有3種邏輯符號,包括:形狀特征型符號(ANSI/IEEEStd 91-1984)、IEC矩形國標(biāo)符號(IEC 60617-12)、DIN符號(DIN 40700)。

ANSI/IEEE Std 91-1984

IEC 60617-12(國標(biāo)符號)

DIN 40700

mos管與門電路圖-CMOS邏輯門電路原理圖

1、高速CMOS電路的電源電壓VDD通常為+5V;Vss接地,是0V。

高電平視為邏輯“1”,電平值的范圍為:VDD的65%~VDD(或者VDD-1.5V~VDD)。低電平視作邏輯“0”,要求不超過VDD的35%或0~1.5V。+1.5V~+3.5V應(yīng)看作不確定電平。在硬件設(shè)計中要避免出現(xiàn)不確定電平。

近年來,隨著亞微米技術(shù)的發(fā)展,單片機(jī)的電源呈下降趨勢。低電源電壓有助于降低功耗。VDD為3.3V的CMOS器件已大量使用。在便攜式應(yīng)用中,VDD為2.7V,甚至1.8V的單片機(jī)也已經(jīng)出現(xiàn)。將來電源電壓還會繼續(xù)下降,降到0.9V,但低于VDD的35%的電平視為邏輯“0”,高于VDD的65%的電平視為邏輯“1”的規(guī)律仍然是適用的。

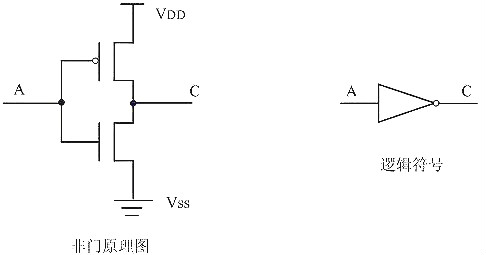

2、非門

非門(反向器)是最簡單的門電路,由一對CMOS管組成。其工作原理如下:

A端為高電平時,P型管截止,N型管導(dǎo)通,輸出端C的電平與Vss保持一致,輸出低電平;A端為低電平時,P型管導(dǎo)通,N型管截止,輸出端C的電平與VDD一致,輸出高電平。

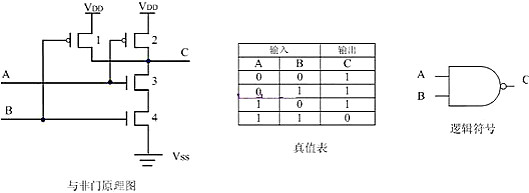

3、與非門

與非門工作原理:

①、A、B輸入均為低電平時,1、2管導(dǎo)通,3、4管截止,C端電壓與VDD一致,輸出高電平。

②、A輸入高電平,B輸入低電平時,1、3管導(dǎo)通,2、4管截止,C端電位與1管的漏極保持一致,輸出高電平。

③、A輸入低電平,B輸入高電平時,情況與②類似,亦輸出高電平。

④、A、B輸入均為高電平時,1、2管截止,3、4管導(dǎo)通,C端電壓與地一致,輸出低電平。

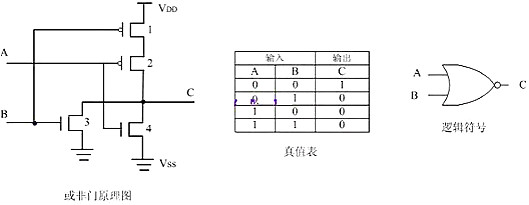

4、或非門

或非門工作原理:

①、A、B輸入均為低電平時,1、2管導(dǎo)通,3、4管截止,C端電壓與VDD一致,輸出高電平。

②、A輸入高電平,B輸入低電平時,1、4管導(dǎo)通,2、3管截止,C端輸出低電平。

③、A輸入低電平,B輸入高電平時,情況與②類似,亦輸出低電平。

④、A、B輸入均為高電平時,1、2管截止,3、4管導(dǎo)通,C端電壓與地一致,輸出低電平。

注:

將上述“與非”門、“或非”門邏輯符號的輸出端的小圓圈去掉,就成了“與”門、“或”門的邏輯符號。而實現(xiàn)“與”、“或”功能的電路圖則必須在輸出端加上一個反向器,即加上一對CMOS管,因此,“與”門實際上比“與非”門復(fù)雜,延遲時間也長些,這一點(diǎn)在電路設(shè)計中要注意。

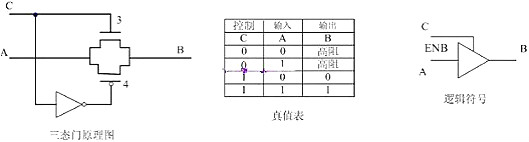

5、三態(tài)門

三態(tài)門的工作原理:

當(dāng)控制端C為“1”時,N型管3導(dǎo)通,同時,C端電平通過反向器后成為低電平,使P型管4導(dǎo)通,輸入端A的電平狀況可以通過3、4管到達(dá)輸出端B。

當(dāng)控制端C為“0”時,3、4管都截止,輸入端A的電平狀況無法到達(dá)輸出端B,輸出端B呈現(xiàn)高電阻的狀態(tài),稱為“高阻態(tài)”。這個器件也稱作“帶控制端的傳輸門”。帶有一定驅(qū)動能力的三態(tài)門也稱作“緩沖器”,邏輯符號是一樣的。

6、組合邏輯電路

“與非”門、“或非”門等邏輯電路的不同組合可以得到各種組合邏輯電路,如譯碼器、解碼器、多路開關(guān)等。

組合邏輯電路的實現(xiàn)可以使用現(xiàn)成的集成電路,也可以使用可編程邏輯器件,如PAL、GAL等實現(xiàn)。

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點(diǎn)擊右邊的工程師,或者點(diǎn)擊銷售經(jīng)理給您精準(zhǔn)的報價以及產(chǎn)品介紹

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點(diǎn)擊右邊的工程師,或者點(diǎn)擊銷售經(jīng)理給您精準(zhǔn)的報價以及產(chǎn)品介紹