MOS集成電路ESD靜電防護介紹

MOS(金屬氧化物半導體)集成電路憑借其高集成度優勢,在電子領域廣泛應用,但其敏感的氧化層結構使其對靜電放電(ESD)極為 “脆弱”。ESD 事件輕則致 MOS 器件性能下滑,重則引發設備徹底報廢。因此,全方位、多層次的 ESD 防護措施至關重要。

MOS(金屬氧化物半導體)集成電路憑借其高集成度優勢,在電子領域廣泛應用,但其敏感的氧化層結構使其對靜電放電(ESD)極為 “脆弱”。ESD 事件輕則致 MOS 器件性能下滑,重則引發設備徹底報廢。因此,全方位、多層次的 ESD 防護措施至關重要。

一、設計階段:筑牢 ESD 防護根基

1.ESD 保護結構:在芯片關鍵部位,如 I/O 端口、電源和地線,嵌入硅基二極管、多層金屬互連、ESD 防護二極管等保護結構,為芯片構筑起抵御 ESD 的 “第一道防線”。

2.井區隔離:運用隔離井區(wells)對不同功能電路區域進行隔離,削弱 ESD 事件對敏感區域的沖擊波及能量影響。

3.器件布局:精心規劃芯片上器件布局,將 ESD 保護結構安置于芯片邊緣或 I/O 端口附近,確保其能迅速響應 ESD 事件,為芯片其他核心區域爭取防護時間。

4.電源管理:打造穩健電源管理電路,保障電源電壓在異常波動時,不會突破器件最大額定值,避免因電源異常引發 ESD 損傷。

5.輸入保護:對輸入信號加以保護,利用限流電阻、電壓鉗位二極管等元件,有效吸收與分散 ESD 能量,降低輸入信號受 ESD 干擾失真的風險。

二、制造過程:嚴守 ESD 防護陣地

1.潔凈室環境:芯片制造全程在無塵、恒濕的潔凈室進行,從源頭減少靜電產生幾率,為芯片制造提供 “無靜電隱患” 的物理空間。

2.接地系統:確保制造設備、工作臺接地良好,為靜電提供順暢流向地面的通道,防止靜電在設備與工作臺表面積累,降低 ESD 風險。

3.防靜電材料:廣泛使用防靜電墊、防靜電包裝材料、防靜電工作服等,全方位減少靜電積累,為芯片制造營造 “低靜電” 環境。

4.操作規范:制定嚴謹操作規范,要求操作人員熟練掌握 ESD 危害知識與防護技能,規范操作行為,避免人為引發 ESD 事件。

三、測試和封裝:延續 ESD 防護使命

1.ESD 測試:對 MOS 集成電路執行嚴格 ESD 測試,對照規定 ESD 標準評估其抗靜電性能,確保產品出廠前具備合格的 ESD 防護能力。

2.防靜電設備:測試與封裝環節,啟用離子風扇、靜電消除器等防靜電設備,持續消除環境中靜電,為芯片測試與封裝作業保駕護航。

3.封裝材料:精選具備優良防靜電性能的封裝材料,為芯片穿上 “防靜電外衣”,進一步阻隔外界靜電侵擾。

4.操作培訓:對參與測試和封裝的操作人員開展 ESD 防護培訓,強化其 ESD 防護意識,確保操作流程符合 ESD 防護要求。

四、使用和運輸:加固 ESD 防護防線

1.防靜電包裝:在 MOS 集成電路運輸與存儲全程,采用防靜電包裝材料,為芯片提供持續、穩定的防靜電保護,隔絕運輸途中靜電干擾。

2.操作環境:把控使用環境濕度在合理區間,借助濕度調節設備維持適宜濕度,降低空氣干燥引發靜電的可能,為芯片使用營造 “低靜電風險” 環境。

3.防靜電接地:使用設備時,確保設備與操作人員均實現良好防靜電接地,為靜電提供安全釋放路徑,避免靜電在使用環節損傷芯片。

4.防靜電標識:在產品包裝、設備顯著位置張貼 ESD 防護標識,醒目提示用戶關注 ESD 問題,遵循 ESD 防護指引操作,延長芯片使用壽命。

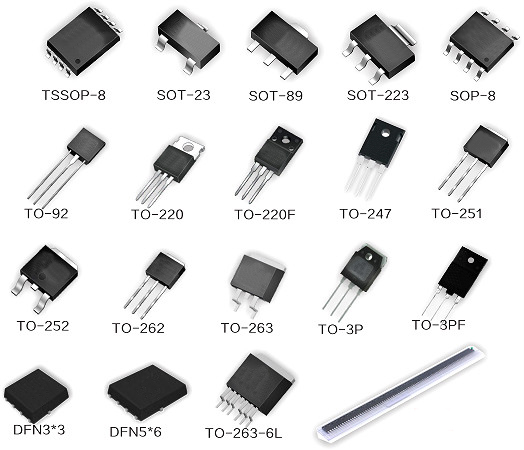

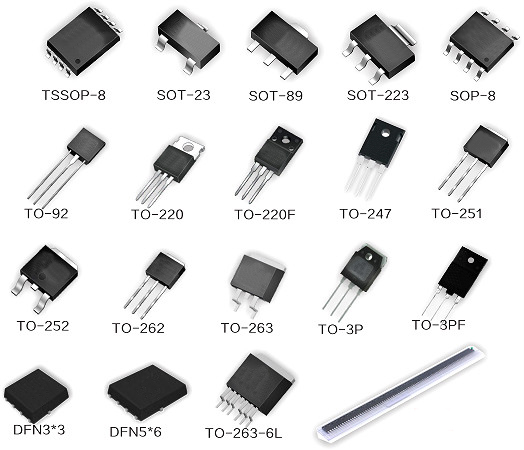

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280