影響MOS器件及其集成電路可靠性的因素很多,有設(shè)計方面的,如材料、器件和工藝等的選取;

有工藝方面的,如物理、化學(xué)等工藝的不穩(wěn)定性;也有使用方面的,如電、熱、機(jī)械等的應(yīng)力和水汽等的侵入等。

從器件和工藝方面來考慮,影響MOS集成電路可靠性的主要因素有三個:一是柵極氧化層性能退化;二是熱電子效應(yīng);三是電極布線的退化。

MOSFET的柵極二氧化硅薄膜是決定器件性能的關(guān)鍵性材料。因為二氧化硅薄膜具有良好的絕緣性,同時它與Si表面接觸的表面態(tài)密度又很低,所以最常用作為柵絕緣層。

柵氧化層一般是采用熱氧化來制備的,良好氧化層的漏電流基本上為0,并且具有較高的擊穿電場強(qiáng)度(擊穿電場強(qiáng)度約為10MV/cm)。

但是,實際上發(fā)現(xiàn),在器件和電路工作時,有時會發(fā)生由于柵氧化層的漏電、并導(dǎo)致?lián)舸┒鸬氖В划a(chǎn)生這種后果的根本原因就是氧化層在電壓作用下性能發(fā)生了退化。

一、柵氧化層性能退化的表現(xiàn):擊穿

在柵極電壓作用下,柵氧化層發(fā)生性能退化的主要表現(xiàn)就是擊穿。

這里存在兩種類型的擊穿:一是瞬時擊穿(TZDB,Tims Zero Dielectic Breakdown),即是加上電壓后就馬上發(fā)生的擊穿——短路;

二是經(jīng)時擊穿(TDDB,Tims Dependent Dielectic Breakdown),即是加上電壓后需要經(jīng)過一段時間之后才發(fā)生的擊穿。

MOSFET和MOS-IC的早期失效往往就包括有柵氧化層的TZDB現(xiàn)象。

TDDB的產(chǎn)生與柵氧化層中的電場(柵電壓)有關(guān)。實驗表明,按照引起擊穿電場的大小,可以把TDDB區(qū)分為三種不同的模式:

①模式A--在較低電場(1MV/cm)時就產(chǎn)生的擊穿;②模式B--在較高電場(數(shù)MV/cm)時產(chǎn)生的擊穿;③模式C--在很高電場(>8MV/cm)時才可能產(chǎn)生的擊穿。

TDDB的模式A往往是由于氧化層中存在針孔等缺陷的緣故,具有這種模式的早期擊穿的芯片,一般都可通過出廠前的篩選而淘汰掉,故模式A擊穿將直接影響到芯片的成品率。

由于氧化層中的針孔等缺陷主要是來自于材料和環(huán)境的污染、微粒之類的雜質(zhì),所以提高材料和工藝的純凈度對于降低出現(xiàn)模式A的幾率、增高成品率具有重要的意義。

TDDB的模式B往往是由于氧化層中存在微量的Na、K等堿金屬和Fe、Ni等重金屬雜質(zhì)的緣故,這些雜質(zhì)離子在較高電場作用下會發(fā)生移動,并且起著陷阱能級的作用。

因此,為了提高模式B的擊穿,也必須嚴(yán)格保證材料和工藝的純凈度,此外還必須注意晶體表面缺陷吸附重金屬雜質(zhì)所產(chǎn)生的不良影響(則需要關(guān)注襯底的結(jié)晶控制技術(shù))。

TDDB的模式C擊穿電壓很高,接近二氧化硅的固有擊穿特性,這是由于氧化層中不存在雜質(zhì)和缺陷的緣故。

二、MOSFET柵氧化層退化的壽命評估

對于帶有經(jīng)時擊穿模式B的不良芯片,需要經(jīng)過較長時間的試驗才能檢測出來,因此必須事先確立器件壽命的檢測和評估方法。

為了保證集成電路能夠正常工作若干年(一般要求10年以上),就需要在出廠前預(yù)測出器件的壽命——壽命評估;這可以通過TDDB試驗預(yù)測出柵氧化層的壽命來確定器件的壽命。

具體的辦法就是采用所謂加速壽命試驗,即把許多器件置于強(qiáng)電場(高于7MV/cm)、溫度為100 0C左右的條件下,觀測器件的經(jīng)時失效率;

一般,柵氧化層的TDDB呈現(xiàn)出兩個區(qū)域:較快擊穿的早期失效區(qū)和需要經(jīng)過很長時間才擊穿的磨損失效區(qū)(二氧化硅的固有擊穿區(qū))。為了不讓器件在出廠后就產(chǎn)生問題,則必須盡量控制器件的早期失效。

對于較厚柵氧化層的器件,發(fā)現(xiàn)早期擊穿的失效率較高,這說明較厚的二氧化硅中含有較多的缺陷。

三、柵氧化層性能退化的機(jī)理

柵氧化層出現(xiàn)性能退化的主要原因是強(qiáng)電場使得柵氧化層產(chǎn)生了漏電、并從而導(dǎo)致的擊穿。

1、在強(qiáng)電場作用下,柵氧化層產(chǎn)生漏電往往是一種常見的現(xiàn)象。

實際上,當(dāng)氧化層中的電場強(qiáng)度大于6MV/cm時,即使是非常優(yōu)質(zhì)的氧化層,也將會產(chǎn)生由于量子效應(yīng)所引起的所謂F-N(Flowler-Nordheim)型隧道電流。

隨著器件尺寸的縮小,氧化層厚度也相應(yīng)地越來越薄(對于LSI而言,一般總是選取柵氧化層厚度為溝道長度的1/50左右),則氧化層的這種F-N型隧道電流也將越來越顯著。

例如,對于厚度為10nm的柵氧化層,在電源電壓為5V時,氧化層中的電場就已經(jīng)大于5MV/cm,所以往往就必須考慮F-N型隧道電流以及所引起的擊穿。

2、柵氧化層的不斷漏電,就會導(dǎo)致氧化層擊穿,這是由于漏電會使得在氧化層中積蓄起很多電荷(正電荷或者負(fù)電荷)的緣故。

因為柵氧化層中往往存在許多陷阱(電子陷阱、空穴陷阱或者中性陷阱),當(dāng)氧化層有隧道電流通過時,則這些陷阱就會俘獲載流子、積蓄起正電荷或者負(fù)電荷,并使得氧化層的局部電場增強(qiáng);

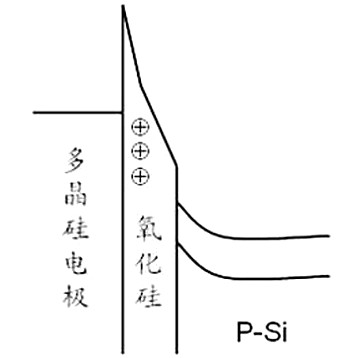

由于電荷積蓄而導(dǎo)致局部電場增強(qiáng)時的能帶圖見圖2和圖3,其中圖1是沒有電荷積蓄時的能帶圖。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報價以及產(chǎn)品介紹