柵氧化層

為了有效地抑制短溝道效應,并保持良好的亞閾值斜率,柵氧化層厚度要和溝道長度以同樣的比例下降。對于0.1μm尺度的CMOS器件,柵氧化層厚度需達到3nm左右。

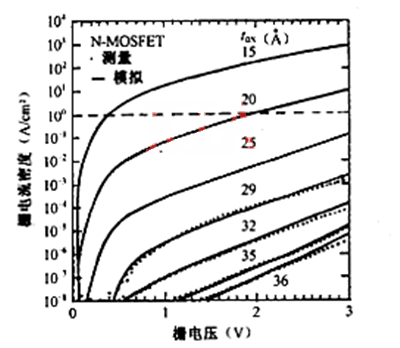

對于超薄氧化層而言,最大的問題是會發(fā)生量子隧道穿通效應。柵氧化層的隧穿電流將隨氧化層厚度的減少量指數(shù)增長,柵偏壓1.5V時,氧化層厚度若從3.6nm降到1.5nm,柵電流密度大約會增長10個數(shù)量級。

氧化層的缺陷

氧化層主要有三個方面的問題:

(1)硅氧化層在靠近硅的附近有很多缺陷,如高密度的電子和空穴陷阱。這些陷阱能引入快界面態(tài),造成偏壓與溫度應力下的電荷不穩(wěn)定性。

(2)硅與二氧化硅的熱膨脹系數(shù)不同而產生了拉伸應力使硅附近氧化層產生較多的缺陷。

(3)普遍認為在硅附近100nm厚的氧化層區(qū)是屬于缺陷較多的區(qū),如氧化層局部生長速率不均勻引起的小斑點和氧化層針孔。

泄漏電流

柵氧化層的泄漏電流通常遠小于器件的導通態(tài)電流,對器件的正常工作不會產生致命的影響,但會對器件的靜態(tài)功耗造成不良影響。

對于下一代納米級CMOS器件,柵有源區(qū)的總面積可能會低于0.1cm2,此時如果電源電壓V∞≈1V的話,柵電流密度的最大允許值應該在1A/cm2的數(shù)量級,由下圖《柵電流密度》可知。

達到這一限制的氧化層厚度為2nm,當氧化層減薄到2nm以下,由隧穿電流引起的CMOS電路芯片的靜態(tài)功耗將達到100mW數(shù)量級,這對于實際應用而言是無法接受的。

換句話說,體硅CMOS溝道長度只能縮小到25~50nm,除非采用新的柵介質材料來取代現(xiàn)用的二氧化硅介質。

動態(tài)隨機存儲器(DRAM)的性能對柵氧化層漏電流更為敏感,因此要求其氧化層的極限厚度更大些。

影響因素

從傳統(tǒng)的角度來看,柵氧化層的減薄會導致電場強度的增加,因而使與時間相關的擊穿(TDDB)更容易發(fā)生,從而縮短器件的壽命。然而,理論和實驗研究結果都證明,對于納米級CMOS器件這個問題并不突出。

原因在于當電源電壓降低到1V左右的時候,跨越氧化層的電子的能量大幅度降低,已不足以對氧化層產生損傷,因此難以發(fā)生TDDB擊穿。至少在氧化的厚度2nm以上的CMOS器件中,TDDB擊穿不構成限制因素。

氧化層減薄引起的另一個問題是反型層電荷的減少,器件跨導會因此而下降,這是由反型層量子化效應和多晶硅姍耗盡效應引起的。

由于反型層量子化效應的存在,反型層電子密度的峰值出現(xiàn)在硅表面以下約1nm處,這將使等效的柵電容減小,進而使有效的反型層電荷減少。

據(jù)估算,由此將導致等效氧化層厚度比氧化層厚度的物理厚度增加0.3~0.4nm。

類似地,多晶硅柵耗盡效應也會引起等效柵電容及反型層電荷的減小。

氧化層越薄,上述兩種效應就越顯著,對于多晶硅摻雜濃度為1020cm-3,氧化層厚度為2nm的CMOS器件,在1.5V的柵壓下,反型層電荷的損失比例大約為20%。

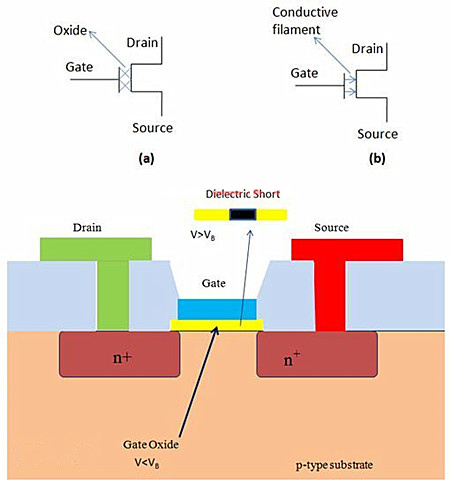

可靠性的降低

MOS晶體管的性能依賴于柵氧化層的厚度。柵氧化層厚度的降低,增強了晶體管的電流驅動能力,提高了速度和功率特性。

因此在工藝縮減中降低柵氧化層厚度可以有效地提高晶體管性能,然而薄的氧化層會加重電流遂穿效應并降低氧化層可靠性。

隨著現(xiàn)代數(shù)字CMOS工藝中柵氧化層厚度達到了幾個分子層(幾納米)的水平,電源電壓被柵氧層的電場所限制”。

電源電壓的變化會使加在柵氧層的電壓高于標稱電壓,降低器件的長期可靠性。需要限制電源和地電壓的過沖,來避免晶體管可靠性的顯著下降。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹